POWER2

| Power Architektúra |

|---|

| NXP (volt Freescale és Motorola) |

| PowerPC e sorozat (2006) ( e200 • e300 • e500 • e600 • e5500 • e6500 ) |

| IBM |

| POWER ISA (1990) • POWER sorozat (1990) |

| IBM-Nintendo együttműködés |

| Gekko • Broadway • Espresso |

| Egyéb |

| Titan • PWRficient • Cell • Xenon • X704 |

| Kapcsolódó hivatkozások |

| OpenPOWER Alapítvány • AIM alliance • RISC • Blue Gene • Power.org • PAPR • PReP • CHRP • AltiVec • tovább... |

Sablon:Power architektúra

|

A POWER2, korábbi elnevezésén RIOS2, egy az IBM által tervezett 32 bites RISC processzor, amely a POWER utasításkészlet-architektúrát implementálja. A POWER2 a POWER1 utódja volt, 1993 szeptemberében mutatkozott be az IBM RS/6000-es rendszereiben. Bevezetése idején a POWER2 volt a leggyorsabb mikroprocesszor, felülmúlva az Alpha 21064-et. 1993-ban azonban megjelent az Alpha 21064A változat, ekkor a POWER2 elvesztette a vezetést és második lett. Az IBM állítása szerint egy 62,5 MHz-en futó POWER2 processzor teljesítménye 73,3 SPECint92 és 134,6 SPECfp92.

A nyílt forráskódú GCC fordítóban a POWER1 (RIOS) és POWER2 (RIOS2) utasításkészletek támogatását a 4.5 verzióban megszüntették.[1]

Leírás

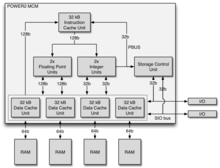

A POWER1-hez képest a processzorban számos fejlesztést hajtottak végre, ezek közé tartozik a továbbfejlesztett utasításkészlet-architektúra, amely új felhasználói és rendszerutasításokat kapott és újabb rendszerjellemzőkkel bővült (négyszavas betöltés/kiírás, nullaciklusos elágazások, hardveres négyzetgyökvonás stb.), a processzor órajelfrekvenciája megnövekedett (55 és 71,5 MHz között lehet), egy helyett két fixpontos egységet és ugyancsak két lebegőpontos egységet tartalmaz, és a gyorsítótárak méretét is megnövelték: a processzor 32 KiB-os utasítás-gyorsítótárat és 128 vagy 256 KiB adat-gyorsítótárat használhat. A POWER2 egy többcsipes kialakítás, amely hat vagy nyolc, részben egyedi integrált áramkörből áll, az adat-gyorsítótár méretétől függően (a 256 KiB konfigurációhoz nyolc csip szükséges). A kialakítás alkotóelemei megegyeznek a POWER1-ével: egy utasítás-gyorsítótár egység, egy fixpontos egység, egy lebegőpontos egység, egy tárvezérlő egység és két vagy négy adat-gyorsítótár egység alkot egy processzort, külön csipekben.

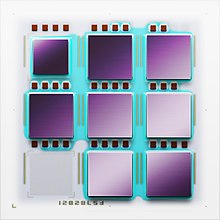

A nyolccsipes konfiguráció összesen 23 millió tranzisztort tartalmaz és az összesített lapkafelület 1215 mm². A csipeket az IBM 0,72 μm-es CMOS folyamatával gyártották,[2] amelyet 0,45 µm-es effektív csatornahossz, egy réteg poliszilícium és négy rétegű fémezés jellemez.[3] A csipek egy 64 mm × 64 mm méretű kerámia többcsipes modulba (multi-chip module, MCM) vannak szerelve.

POWER2+

A POWER2+ a POWER2 egy javított, tranzakciófeldolgozásra optimalizált verziója. 1994 májusában mutatták be. A tranzakciófeldolgozási munkafolyamatok hatékonyságának fokozása céljából 512 KiB, 1 MiB és 2 MiB méretű második szintű gyorsítótárakkal bővítették ki a processzort. Az L2 gyorsítótár tokon kívül helyezkedik el, ipari szabvány burst SRAM-okkal lett megvalósítva. A gyorsítótár a POWER2+ processzorhoz egy 64 bites (alsó kategóriás/belépő szintű rendszerekben) vagy 128 bites (felsőkategóriás rendszerekben) sínen keresztül kapcsolódik. A gyorsítótár közvetlen leképezésű, sorai (line) 128 bájt méretűek és átíró aktualizálást alkalmaz. A gyorsítótár címkéit (tags) a tárvezérlő egység csip tartalmazza. A POWER2+ egy keskenyebb 64 vagy 128 bites memóriasínt és egy kisebb 64 vagy 128 KiB méretű adat-gyorsítótárat tartalmaz. A kisebb gyorsítótár miatt az adat-gyorsítótár egység is kisebb csipeket igényel és az átdolgozott tárvezérlő egység csip szintén kisebb. A cél egy hatcsipes konfiguráció létrehozása volt, a költségek csökkentése érdekében, emiatt a csipek is forrasztógolyós (solder ball connect) (SBC) tokozásba kerültek MCM helyett.

P2SC

A P2SC – a POWER2 Super Chip rövidítése – 1996 októberében jelent meg, mint az a POWER2 utódja. Ez a nyolc-csipes POWER2 egy csipen kivitelezett megvalósítása. 15 millió tranzisztort integrál egy 335 mm² lapkán. Az IBM 0,29 µm-es öt fémezési rétegű CMOS-6S folyamatával gyártották. Az első verzió 120 vagy 135 MHz órajelen működhetett, így közel kétszer olyan gyors, mint a 71,5 MHz-en futó POWER2, miközben a memória és a bemeneti/kimeneti sínek fél órajel-sebességen futnak, ezáltal magasabb órajel-frekvenciát támogathatnak. Az IBM állítása szerint ennek a verziónak a teljesítménye 5,5 SPECint95_base és 14,5 SPECfp95_base volt. Egy gyorsabb, 160 MHz-es órajelű változat is készült, 0,25 µm-es CMOS-6S2 folyamattal, ezt a Microprocessor Forum-on jelentették be 1997 októberében.

A P2SC nem volt a POWER2 tökéletes másolata, az L1 adat-gyorsítótár és az adat-TLB (címfordító gyorsítótár) kapacitását megfelezték, így a gyorsítótár mérete 128 KiB lett, a TLB pedig 256 bejegyzést tartalmaz, és kihagyták belőle egy ritkán használt jellemző, a TLB-ben lévő bejegyzések lezárásának implementációját is, hogy az eredeti kialakítás elférjen egyetlen lapkán.

A P2SC-t a POWER3 követte, az IBM zászlóshajójaként az RS/6000 vonalban, 1998-ban. A P2SC egyik jelentős alkalmazása volt a 30 számítási csomópontot (processzort) tartalmazó IBM Deep Blue szuperszámítógép ill. sakkszámítógép, ami sakkban legyőzte a világbajnok Garri Kaszparovot 1997-ben. Ugyanakkor a számítógép sakkozási képességei inkább a külön erre a célra tervezett egyedi integrált áramköröknek voltak köszönhetők, mint a P2SCs processzoroknak.

Jegyzetek

Fordítás

Ez a szócikk részben vagy egészben a POWER2 című angol Wikipédia-szócikk ezen változatának fordításán alapul. Az eredeti cikk szerkesztőit annak laptörténete sorolja fel. Ez a jelzés csupán a megfogalmazás eredetét és a szerzői jogokat jelzi, nem szolgál a cikkben szereplő információk forrásmegjelöléseként.

Források

További információk

- doi:10.1147/rd.385.0537

- Ball, Richard (15 October 1997). "Chipville USA". Electronics Weekly.

- DeTar, Jim (22 August 1994). "IBM details Power2+; DEC bares new Alpha AXP". Electronic News.

- Gwennap, Linley (4 October 1993). "IBM Regains Performance Lead with Power2". Microprocessor Report.

- Gwennap, Linley (26 August 1996). "IBM Crams POWER2 onto Single Chip". Microprocessor Report.

- doi:10.1147/rd.385.0525

- Lineback, J. Robert (28 June 1993). "IBM readies RISC Progeny in Unix". Electronic News.

- Shippy, David (9 August 1994). "The Power2+ Processor". Hot Chips 6.

- doi:10.1147/rd.385.0503

- Statt, Paul (January 1994). "Power2 Takes the Lead--For Now". Byte.

- doi:10.1147/rd.385.0493